University Of Diyala College Of Engineering Computer Engineering Department

# **Modeling Sequential Logic in VHDL**

Dr. Yasir Amer Abbas Third stage 2017

## IN THIS LECTURE

- Synchronous sequential logic circuits rely on storage elements for their operations.

- Flips-flops (FFs) and latches are two commonly used one-bit elements.

- Others as registers, shift registers, and counters.

- Only synchronous sequential logic is considered.

## LATCHES & FLIP-FLOPS

- A latch is a level-sensitive memory device (transparent).

- As long as the pulse remains at the active high level, any changes in the data input will change the state of the latch.

- A flip-flop (FF) is an edge-triggered memory device.

- An edge-triggered FF ignores the pulse while it is at a constant level (non-transparent).

- Triggers only during a transition of the clock signal.

- Could on the positive edge of the clock (posedge), or negative edge (negedge).

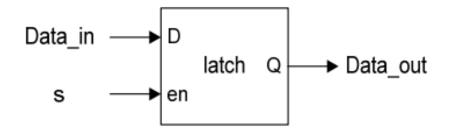

# SIMPLE LATCH

## D Latch

- $\cdot\,$  A latch is inferred because the IF statement is incomplete.

- $\cdot\,$  The notion of implied memory is instantiated in this case.

```

...

always (S or Data_In)

if ( S )

Data_out = Data_In;

```

```

••••

```

# SIMPLE LATCH

```

library ieee;

use ieee.std_logic_1164.all;

entity D_latch is

port(

data_in: in std_logic;

enable: in std_logic;

data_out: out std_logic );

end D_latch;

architecture behv of D_latch is

begin -- compare this to D flipflop

process(data_in, enable)

begin

if (enable='1') then -- no clock signal here

data_out <= data_in;

end if;

end process;

end behv;

```

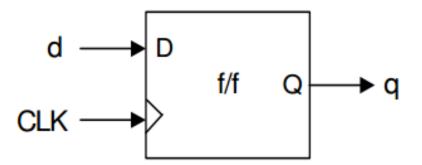

## BASIC POSITIVE-EDGE TRIGGERED D FLIP-FLOP

## FLIP-FLOP IS THE BASIC COMPONENT

```

library ieee ;

use ieee.std_logic_1164.all;

```

```

entity dff is

port(

data_in: in std_logic;

clock: in std_logic;

data_out: out std_logic );

end dff;

Architecture behv of dff is

begin

process(data_in, clock).

begin

-- clock rising edge

if (clock='1' and clock'event) then

data_out <= data_in;</pre>

end if;

end process;

end behv;

```

## VHDL CODE FOR RISING EDGE D FLIP FLOP

Library IEEE; USE IEEE.Std\_logic\_1164.all;

entity RisingEdge\_DFlipFlop is

port(

Q: out std\_logic; Clk:in std\_logic; D:in std\_logic);

## end RisingEdge\_DFlipFlop;

Architecture Behavioral **of** RisingEdge\_DFlipFlop **is begin**

```

process(Clk)

begin

if(rising_edge(Clk)) then

Q <= D;

end if;

end process;

end Behavioral;

```

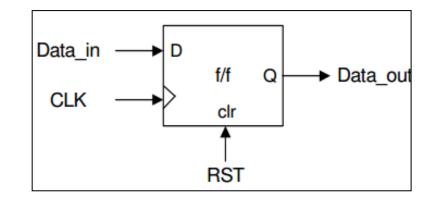

## VHDL CODE FOR RISING EDGE D FLIP-FLOP WITH SYNCHRONOUS RESET

#### Library IEEE; USE IEEE.Std\_logic\_1164.all; entity RisingEdge\_DFlipFlop\_SyncReset is port(

```

Q : out std_logic;

Clk :in std_logic;

sync_reset: in std_logic;

D :in std_logic );

end RisingEdge_DFlipFlop_SyncReset;

```

Architecture Behavioral **of** RisingEdge\_DFlipFlop\_SyncReset **is begin**

```

process(Clk)

begin

if(rising_edge(Clk)) then

if(sync_reset='1') then

Q \le 0';

else Q \le D;

end if;

end j;

end process;

end Behavioral;

```

### VHDL CODE FOR RISING EDGE D FLIP-FLOP WITH ASYNCHRONOUS RESET HIGH LEVEL

Library IEEE; USE IEEE.Std\_logic\_1164.all;

entity RisingEdge\_DFlipFlop\_AsyncResetHigh is

port(

$Q: \boldsymbol{out} \ std\_logic;$

Clk :in std\_logic;

Async\_reset: in std\_logic;

D : in std\_logic );

#### end RisingEdge\_DFlipFlop\_AsyncResetHigh;

Architecture Behavioral of RisingEdge\_DFlipFlop\_AsyncResetHigh is begin

process(Clk, Async\_reset) .

begin

```

if(Async_reset='1') then Q <= '0';

elsif(rising_edge(Clk)) then

Q <= D;

end if;

end process;

```

end Behavioral;

10

## N-BIT REGISTER

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

entity ckt\_reg is

```

generic (pattern : natural := 4);

```

Port ( clk : in STD\_LOGIC;

rst : in STD\_LOGIC; loadEn : in STD\_LOGIC; reg\_in : in STD\_LOGIC\_VECTOR (regCount-1 downto 0); reg\_out : out STD\_LOGIC\_VECTOR (regCount-1 downto 0));

end ckt\_reg;

```

architecture Behavioral of ckt\_reg is

```

begin

```

process (clk, rst)

begin

if rst = '1' then

reg _out <= '0';

elsif clk'event and clk = '1' then

if loadEn = '1' then

reg _out <= reg_in;

end if;

end if;

end if;

end process;</pre>

```

## SIMULATION N BIT REGISTER

|                                     | 12 21 | Î F    | 4 IC 1 | 71 🎤 | P.P.  | XX      | E     | 11       |        | ₽×   | 1000 | ~    | ns     | <b>×</b> |        |       |        |      |        |       |       |      |     |  |

|-------------------------------------|-------|--------|--------|------|-------|---------|-------|----------|--------|------|------|------|--------|----------|--------|-------|--------|------|--------|-------|-------|------|-----|--|

| Current Simulation<br>Time: 4000 ns |       | 0 1000 |        |      |       |         |       |          |        |      |      | 2    | 2000   |          |        |       |        |      |        |       |       |      |     |  |

| olk cik                             | 1     |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      |        |       |       |      |     |  |

| o, I rst                            | 0     |        |        |      |       | 90-<br> |       | эс.<br>- |        |      |      |      |        | *        |        |       |        |      |        |       | - 12  |      |     |  |

| o loadEn                            | 0     |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      |        |       |       |      |     |  |

| 🖬 🚮 reg_in[3:0]                     | 4     |        | 4'b000 | 0    | X 4't | 0011    | 4'b0  | )101     | ₹ 4"b1 | 1100 | 4'b1 | 110  | 4'b1   | 000      | 4'b01  | 100 🗴 | 4'b1   | 011  | 4'b1(  | 010   | X     | 4'b0 | 111 |  |

| 🖪 🚮 reg_out[3:0]                    | 4     | 4)     |        | 4'b0 | 000   |         | X 4'b | 0101     | 4'b    | 1100 | 4"b  | 1110 | ( 4'b1 | 1000     | ( 4'b0 | 100   | ( 4'b1 | 1011 | ( 4'b1 | 010   | X     |      |     |  |

| PERIOD[31:0]                        | 3     |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      | 3      | 2'h0( | 00000 | C8   |     |  |

| DUTY_CYCLE                          | 0.5   |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      |        |       | 0.5   |      |     |  |

| OFFSET[31:0]                        | 3     |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      | 3      | 2'h0  | 00000 | 64   |     |  |

|                                     |       |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      |        |       |       |      |     |  |

|                                     |       |        |        |      |       |         |       |          |        |      |      |      |        |          |        |       |        |      |        |       |       |      |     |  |

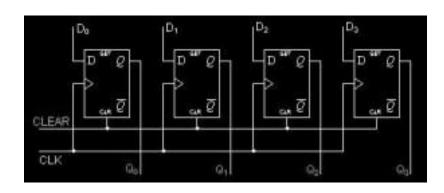

## PARALLEL IN – PARALLEL OUT SHIFT REGISTERS

library ieee;

use ieee.std\_logic\_1164.all;

#### entity pipo is

#### port(

```

clk : in std_logic;

D: in std_logic_vector(3 downto 0);

Q: out std_logic_vector(3 downto 0)

);

end pipo;

```

architecture arch of pipo is

#### begin

process (clk)

begin

```

if (CLK'event and CLK='1') then

```

$Q \ll D;$

end if;

end process;

end arch;

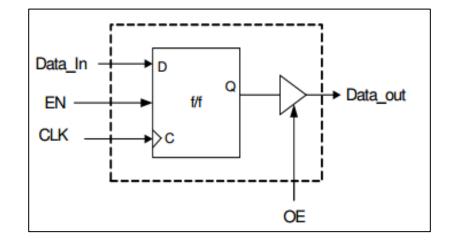

# H.W: DESIGN FLIP-FLOP WITH A TRI-STATE OUTPUT USING VHDL CODE

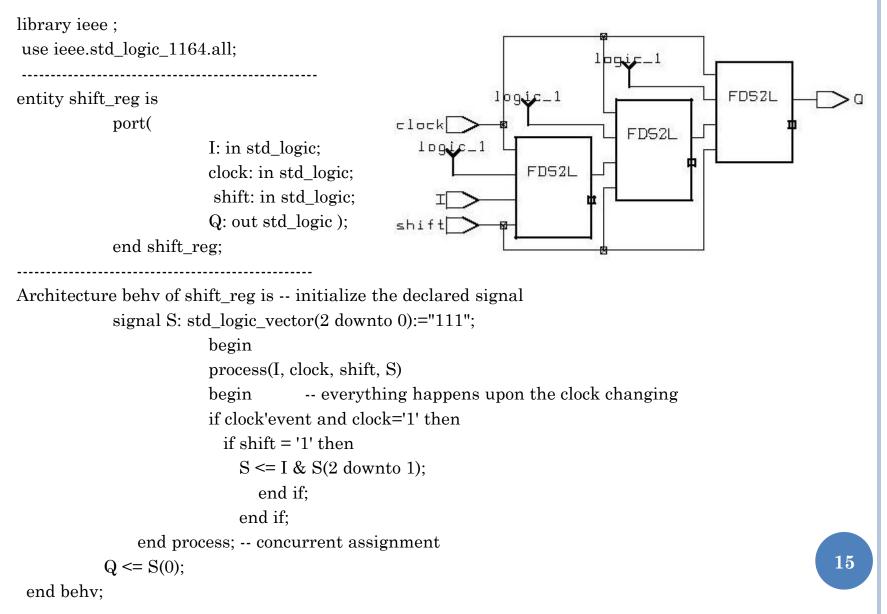

## SHIFT REGISTER

# SIMULATION WAVEFORM SHIFT REGISTER

| 😹 Waveform Ed                     | itor 1 *                |                             |                                                     | _ 🗆 🗙   |

|-----------------------------------|-------------------------|-----------------------------|-----------------------------------------------------|---------|

| <u>File E</u> dit Sea <u>r</u> cł | n <u>V</u> iew <u>[</u> | <u>D</u> esign <u>S</u> imu | ılation <u>W</u> aveform <u>T</u> ools <u>H</u> elp |         |

|                                   | h R 🕨                   | 0 00 1                      | Q M. Q. Q. Q. Q. M. M. H. 🕅                         | en ne 🛸 |

| Name                              | Value                   | Stimulator                  | i 20 i 40 i 60 i 80 i 100 i 120 i 140               | 150 ns  |

| ™ T_clock                         | 0                       |                             |                                                     |         |

| ™ T_shift                         | 1                       |                             |                                                     |         |

| ∿ T_I                             | 1                       |                             |                                                     |         |

| ™ T_Q                             | 1                       | -                           |                                                     |         |

|                                   |                         |                             |                                                     |         |

|                                   |                         |                             |                                                     |         |

|                                   |                         |                             |                                                     |         |

|                                   |                         |                             |                                                     | ·       |

|                                   |                         |                             | <b>۱</b>                                            | + + 0 + |

| Ready                             |                         |                             |                                                     |         |

# COUNTER

library ieee ;

use ieee.std\_logic\_1164.all; use ieee.std\_logic\_unsigned.all;

```

-----

entity counter is

generic(n: natural :=2);

port(

clock: in std_logic;

clear: in std_logic;

count: in std_logic;

Q: out std_logic_vector(n-1 downto 0) );

end counter;

architecture behv of counter is

signal Pre_Q: std_logic_vector(n-1 downto 0);

begin -- behavior describe the counter

process(clock, count, clear)

begin

if clear = '1' then Pre_Q <= Pre_Q - Pre_Q;

elsif (clock='1' and clock'event) then

if count = '1' then Pre_Q <= Pre_Q + 1;

end if:

end if;

end process; -- concurrent assignment statement

Q \leq Pre_Q;

end behv;

```

| COUNTH                | ER                                                               |                |    |     |

|-----------------------|------------------------------------------------------------------|----------------|----|-----|

|                       |                                                                  | clock          |    | :0] |

| ∰ ₩aveform Editor 1 * |                                                                  |                |    |     |

|                       | n <u>S</u> imulation <u>W</u> aveform <u>T</u> ools <u>H</u> elp | «              |    |     |

| 🖻 🖬 👗 🖬 🛍 🗠 <         |                                                                  | 🧏 🛨 Tit 🦛 📌 📩  |    |     |

| Name Value Stimulator | 1 · 20 · 1 · 40 · 1 · 60 · 1 · 80 · 1 · 100 ·                    | 1 · 120 140 ns |    |     |

| P clock 0 Clock       |                                                                  |                |    |     |

| P-clear 0 A           |                                                                  |                |    |     |

| Procunt 1 Z           |                                                                  |                |    |     |

| ⊞ ™ Pre_Q 0           |                                                                  |                |    |     |

| <b>⊕ − Q</b> 0        | <u>(0 ) (1 )(2 )(3 )(0 )(1 )(2)(0 )(1</u>                        |                |    |     |

|                       |                                                                  |                | 18 |     |

| Ready                 |                                                                  |                |    |     |

## Finite State Machine (FSM)

$\cdot\,$  A circuit type with memory.

$\cdot\,$  Usually as datapath controller unit.

$\cdot\,$  Via algorithmic state machine (ASM) flowchart, an FSM is readily modeled in HDL.

$\cdot\,$  There are two basic models of FSMs: Moore and Mealy.

$\cdot\,$  In a Mealy machine, the next state (NS) and the outputs depend on both the present state (PS) and the inputs.

• The NS of a Moore machine depends on the PS and the inputs, but the outputs depend on only the PS.

$\cdot\,$  All FSMs have the general feedback structure.

$\cdot$  We will deal only with synchronous FSMs, hence the state transitions of the machine are synchronized by the active edge of a common clock.

In this case, the state register is consisted of edge triggered flipflops.